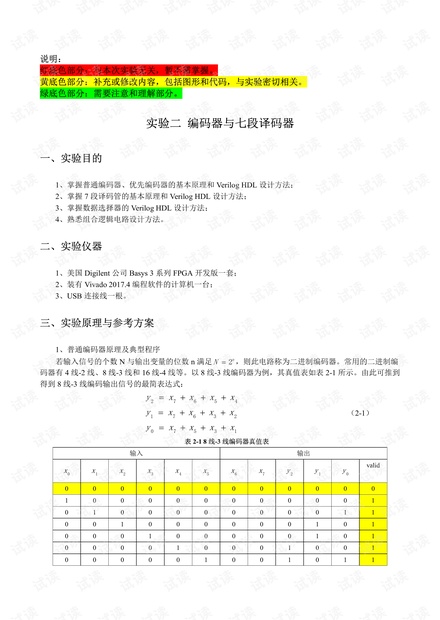

编码器与七段译码器是数字电路中的基本元件,它们在数据处理和显示方面发挥着重要作用。本实验的目的是让学生掌握普通编码器、优先编码器和七段译码管的基本原理和使用Verilog HDL进行设计的方法。学生将学会编写Verilog HDL代码来实现这些功能,并通过实践加深对组合逻辑电路设计方法的理解。 实验仪器包括Digilent公司Basys3系列FPGA开发板、安装有Vivado 2017.4编程软件的计算机以及USB连接线。FPGA(现场可编程门阵列)是一种可以通过软件重新配置的半导体设备,非常适合用于实验和原型设计。 普通编码器是一种将多个输入信号编码成二进制输出的组合逻辑电路。以8线-3线编码器为例,它将8个输入信号编码成3个输出信号。编码器的基本原理可以通过真值表来表示,真值表显示了所有可能的输入信号与相应的输出信号之间的关系。在Verilog HDL中,编码器可以通过逻辑方程或循环语句来实现。逻辑方程方法直接根据真值表来编写对应的逻辑表达式;循环语句方法则通过遍历所有输入信号来找出有效信号并进行编码。 优先编码器与普通编码器的主要区别在于其输入信号的优先级。当存在多个高电平输入时,优先编码器总是对具有最高优先级的信号进行编码。在真值表中,具有最高优先级的信号位于主对角线上。优先编码器的Verilog HDL实现类似于普通编码器,但循环语句中对输入信号的遍历顺序决定了哪个输入具有优先级。 七段译码器是一种将二进制信号转换为七段LED显示管的控制信号的设备。它有7个LED段,以及一个可选的小数点LED。七段译码器分为共阳极和共阴极两种类型,这取决于LED的连接方式。在共阳极数码管中,所有的阳极连接在一起形成公共阳极,当公共阳极COM接到逻辑高电平时,相应字段的阴极为低电平则LED会点亮。相反,当阴极为高电平时,LED熄灭。 在Verilog HDL中实现七段译码器时,需要将4位二进制数作为输入,并生成控制七个LED段的逻辑信号,同时考虑是否需要点亮小数点LED。七段译码器的功能表详细描述了输入二进制数与七段LED显示状态之间的关系。 整体而言,本实验通过对编码器和七段译码器的设计,帮助学生理解和掌握数字逻辑电路的设计思想,同时提高了学生在实际应用中使用Verilog HDL编写代码的能力。通过这些基础实验,学生可以为后续更复杂的数字系统设计打下坚实的基础。

剩余11页未读,继续阅读

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 英语日常词汇分类.doc

- 英语动词单三变化规则与名词单数变复数口诀.doc

- 幼教、少儿创新教育课程《快乐记忆》系列课程市场运营方案报告.doc

- 在阳光中奔跑[800字]作文.doc

- 语文必修三理解性默写填空.doc

- 中考语文答题套路(人版).doc

- 中学课程设置方案.doc

- 家庭教育及亲子沟通公益讲座讲稿.doc

- 综合实践我国象棋教学案.doc

- 不安全化学品储罐区隐患排查表.doc

- 教师行为规范心得体会.doc

- 建设工程合同模板管理试题A卷与答案.doc

- 科教版八年级物理(上册)期末测试题及答案.doc

- 牛津高中英语模块一至模块十一短语.doc

- 鲁迅的儿童教育思想-王敏.doc

- H3C SecPath F1000F5000FW插卡vFW系列防火墙 命令参考(V7)(R8X60-R9X60-E8X60-E9X60-E1185)-6W614

信息提交成功

信息提交成功