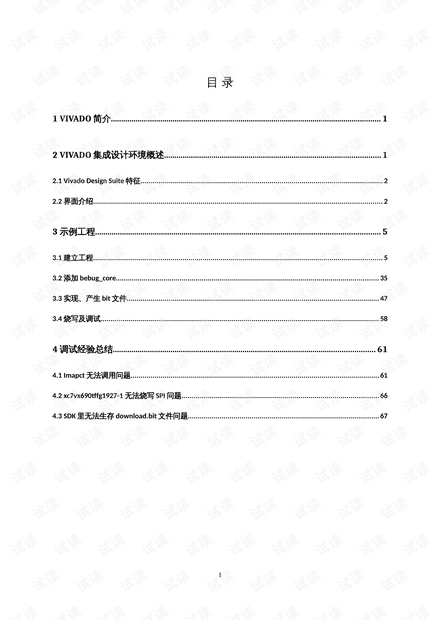

超级详细的VIVADO使用指导教程,step by step讲解从开始建立工程,新建代码文件,导入文件,生成IP,导入IP等等,到最后生成代码文件,下载到板卡调试等步骤,每一步都有详细图文教程,适合新手,少走弯路 ### Vivado开发工具使用指导书知识点详述 #### 一、Vivado简介与特性 **1.1 Vivado设计套件概述** - **发布时间**:由FPGA领军企业赛灵思(Xilinx)于2012年推出。 - **核心特点**:集成了系统级到IC级别的设计工具,并基于共享的可扩展数据模型和统一的调试环境构建。 - **开放性**:兼容多种业界标准如AMBA AXI4互联规范、IP-XACT IP封装元数据、TCL脚本语言、Synopsys系统约束(SDC)等,方便用户根据需求定制设计流程。 **1.2 Vivado设计套件的核心优势** - **集成组件**:针对集成瓶颈,采用ESL设计进行C语言算法IP的快速综合与验证,提高系统验证的仿真速度高达3倍,硬件协同仿真的性能提升100倍。 - **实现组件**:解决实现瓶颈,采用分层器件编辑器和布局规划器、逻辑综合工具,提高速度4倍以上,以及具备时序分析技术的“成本”函数最小化工具。 - **灵活性与效率**:支持增量式流程,仅需对设计的一部分进行重新实现即可快速响应工程变更,同时保持性能稳定。 - **预估与优化**:利用共享的数据模型预估功耗、时序和面积,优化自动化时钟门控等高级功能。 #### 二、Vivado集成设计环境概述 **2.1 Vivado IDE 开发模式** - **Project Mode**:通过图形界面创建工程,完成综合、实现并生成比特流(bitstream)。这种方式直观易学,适用于大多数设计任务。 - **Non-Project Mode**:使用TCL命令行来完成工程的创建、综合等功能。这种方式相对较少被使用。 **2.2 Vivado Design Suite 特征** - **工业设计标准支持**:支持TCL、AXI4、IP-XACT、Synopsys design constraints (SDC)等多种工业标准。 - **设计语言**:支持Verilog、VHDL、SystemVerilog、SystemC、C/C++等多种设计语言。 - **IP Integrator替代Xilinx Platform Studio (XPS)**:在Vivado集成设计环境中,IP Integrator成为主要的IP集成工具,但仍然支持XPS的使用。需要注意的是,Zynq芯片的开发不再支持XPS。 **2.3 Vivado IDE 功能介绍** - **I/O Pin Planning and Floorplanning**:实现管脚布局的优化,提高设计实现的质量。(参考资料:UG899 和 UG906) - **Design Analysis and Verification**:在设计的不同阶段进行仿真、验证和调试。(参考资料:UG900 和 UG906) - **Device Programming and Hardware Validation**:支持设备编程和硬件验证功能。(参考资料:UG908) #### 三、示例工程详解 **3.1 建立工程** - **创建新工程**:通过Vivado IDE的图形界面创建新项目,指定项目名称和位置。 - **设置目标硬件**:选择目标FPGA型号,例如XC7VX690TFFG1927-1。 - **添加源文件**:将设计文件(如Verilog或VHDL)添加到项目中。 - **配置工具选项**:根据具体需求配置综合、实现和验证选项。 **3.2 添加debug_core** - **添加Debug Core**:通过添加Debug Core IP核来支持调试功能。 - **配置Debug Core**:配置Debug Core的相关参数,如JTAG接口设置。 **3.3 实现与生成bit文件** - **综合与实现**:自动完成综合和实现过程,生成比特流文件。 - **生成bit文件**:导出最终的比特流文件用于编程。 **3.4 烧写及调试** - **烧写操作**:使用Vivado IDE或外部工具(如Impact)将比特流文件烧写到FPGA。 - **调试**:通过集成的调试工具进行硬件调试,确保设计的正确性和功能性。 #### 四、调试经验总结 **4.1 Impact无法调用问题** - **常见原因**:可能是由于软件版本不匹配、驱动程序未安装或配置不正确等原因导致。 - **解决方案**:确保所有软件和驱动都已正确安装且版本兼容。 **4.2 xc7vx690tffg1927-1无法烧写SPI问题** - **可能原因**:SPI接口配置不正确、SPI Flash未正确连接等。 - **解决办法**:检查SPI配置是否准确无误,确保SPI Flash与FPGA之间的连接正确。 **4.3 SDK里无法生存download.bit文件问题** - **原因分析**:可能是由于SDK与Vivado版本不匹配、配置错误等原因导致。 - **解决方法**:确认SDK和Vivado版本兼容性,并检查生成比特流文件所需的配置是否正确。 #### 五、界面介绍 **5.1 运行环境要求** - **操作系统**:64位操作系统。 - **内存要求**:足够的内存空间以避免运行时出现内存不足的错误。 **5.2 启动Vivado** - **启动路径**:安装完成后,通过特定路径启动Vivado工具。 - **主界面**:启动后的Vivado IDE主界面。 **5.3 流程导航器** - **功能概述**:流程导航器帮助用户管理设计流程中的各个步骤,提供清晰的操作指引。 ### 总结 Vivado作为一款强大的FPGA设计工具,不仅拥有丰富的功能,还支持多种工业标准和设计语言。通过本篇指南,读者可以了解到如何使用Vivado创建工程、添加源文件、生成bit文件以及进行调试等关键步骤。无论是对于初学者还是有经验的设计者来说,这都是一个非常有用的资源。希望本篇指导书可以帮助您更高效地使用Vivado进行FPGA开发工作。

剩余63页未读,继续阅读

- 粉丝: 1

- 资源: 5

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【新增】-140 -医美医院-全岗位薪酬方案(实用篇).doc

- 【新增】-146 -制药公司薪酬制度.doc

- 【新增】-145 -证券薪酬管理制度.doc

- 【新增】-144 -证券薪酬管理手册.doc

- 【新增】-150 -中小公司薪资方案.doc

- 【新增】-147 -制药有限公司薪酬体系设计.doc

- 【新增】-148 -制造生产薪酬体系方案及对策.doc

- 【新增】-005 -餐饮店员工薪酬制度与考核方案.docx

- 【新增】-006 -餐饮公司薪酬管理体系.docx

- 【新增】-012 -传媒公司薪酬方案.docx

- 【新增】-021 -店铺人员薪酬方案.docx

- 【新增】-019 -电子商务公司薪资体系.docx

- 【新增】-017 -电商运营体系薪酬激励与绩效考核方案.docx

- 【新增】-022 -房产中介薪酬管理规定.docx

- 【新增】-029 -服装店门店薪酬绩效考核方案.docx

- 【新增】-034 -服装行业终端导购薪资方案.docx

信息提交成功

信息提交成功