基于FPGA(现场可编程门阵列)和DSP(数字信号处理器)的雷达信号处理模块设计,是在提高雷达系统性能和稳定性方面的一种重要技术手段。本文将详细介绍FPGA与DSP相结合在雷达信号处理中的应用及其模块化设计。

FPGA和DSP均是现代雷达信号处理领域的重要硬件平台。FPGA具有高度可编程性和并行处理能力,适合完成复杂逻辑运算和实时信号处理;而DSP则以高性能的数学运算能力和快速的指令周期而著称,适合于实现各种数字滤波、变换及算法运算。结合二者的优势,可以在雷达信号处理过程中发挥各自特长,实现更高的处理效率和更低的功耗。

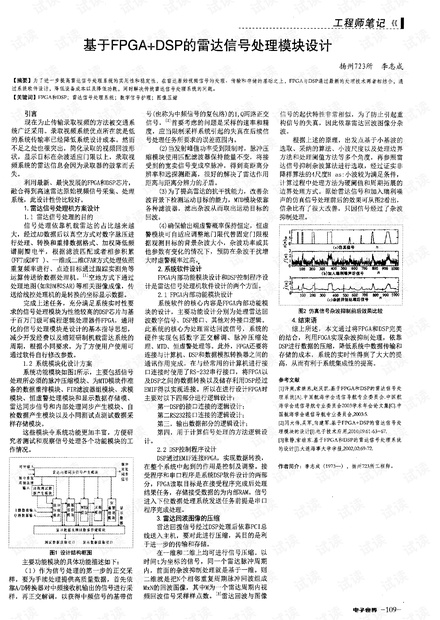

在雷达信号处理的目标方面,雷达系统的主要任务是通过信号采集、处理、传输和存储来获取和分析目标信息。原始视频信号经过A/D转换后,FPGA和DSP可以联合工作,对数据进行有效的数字脉压处理、转换和重排,以及滤波匹配和相参积累。在此基础上,通过一维或二维CFAR处理,提高雷达的检测能力。此外,对于空地方式,还能进行图像成像处理,将数据转换为坐标显示数据。

系统模块化设计是本方案的另一关键部分,通过将雷达信号处理系统划分为多个功能模块,如脉冲压缩模块、数据重排模块、FIR滤波器组模块、求模模块、恒虚警处理模块等,使得系统结构更加灵活,便于扩展和维护。这些模块各自负责不同的处理任务,配合工作,确保整个雷达信号处理系统的稳定和高效运行。

在FPGA内部功能模块设计方面,主要功能包括数字正交解调、脉冲压缩处理、MTD(动目标检测)和恒虚警处理等。此外,FPGA还需要实现与计算机、DSP以及其他设备之间的通信,例如使用RS-232串行接口进行通信。在DSP控制程序设计方面,DSP通过EMIF接口连接FPGA,进行数据转换和处理,控制整个信号处理流程。

雷达回波图像的压缩技术也是雷达信号处理中的一个重要环节。通过DSP处理后的雷达回波信号,可以使用PCI总线传输到主机进行进一步的分析和显示。图像压缩技术的应用可以有效减少数据传输量,降低对存储和传输资源的需求。

基于FPGA+DSP的雷达信号处理模块设计方案,不仅提高了雷达信号处理的效率和性能,还通过模块化设计增强了系统的通用性和灵活性。通过正交采样、脉冲压缩、MTD、恒虚警处理等关键技术,系统能有效地处理雷达信号,提高雷达对目标的探测和跟踪能力,同时通过图像压缩技术减小数据存储量和提高数据传输效率。整个设计过程充分考虑了实时性要求,确保了系统运行的稳定性和可靠性。