正弦信号发生器是电子和信号处理领域中一种基础且关键的设备,它用于产生不同频率和幅度的纯正弦波信号。而数字直接合成(DDS)技术是一种先进的数字波形合成方法,它利用数字技术直接合成出所需的信号,因而具有频率切换速度快、频率分辨率高和相位噪声低等特点。现场可编程门阵列(FPGA)是一种可以通过编程来配置门阵列的集成电路,其内部包含大量的可编程逻辑单元和可编程互连,具有高度的灵活性和极快的处理速度。

将FPGA技术应用于DDS正弦信号发生器中,可以实现信号频率的快速切换和高精度控制。FPGA作为DDS技术的硬件载体,能够通过编程实现DDS算法,将数字形式的信号转换为模拟正弦波信号。

正弦信号发生器在无线通信、雷达、声纳、仪器校准和电子测试等领域有广泛的应用。基于FPGA的DDS正弦信号发生器,一方面可以利用FPGA的可编程特性,灵活地修改信号参数和信号处理算法,以适应不同应用场合的需求;另一方面,FPGA的并行处理能力,使得其能够实时产生连续的、高质量的正弦波信号,非常适合用于高速信号处理和实时信号生成。

设计基于FPGA的DDS正弦信号发生器时,涉及到的关键技术包括:

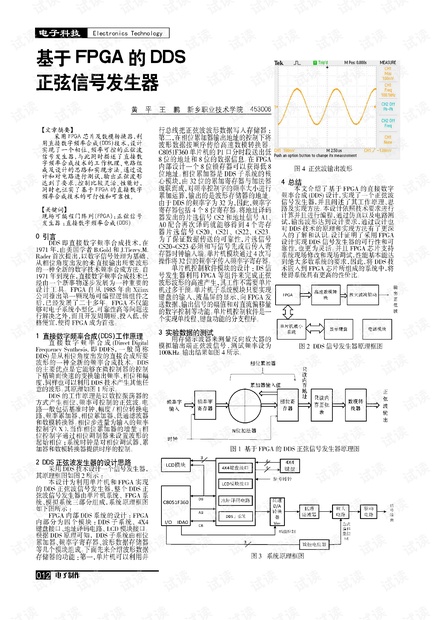

1. DDS算法的实现:DDS算法的核心在于相位累加器和波形查找表(LUT)。相位累加器根据频率控制字以一定的速率对相位进行累加,产生不同的相位值。波形查找表用于将这些相位值映射成对应的正弦波幅度值。

2. 波形查找表的设计:在FPGA内部设计存储正弦波样本数据的波形查找表,通常是一个只读存储器(ROM)或随机存取存储器(RAM)。设计时要考虑查找表的大小和精度,以及如何通过查找表输出连续的波形样本。

3. 数模转换:虽然FPGA可以处理数字信号,但许多应用场合需要模拟信号输出。因此,设计时需要包括数字到模拟转换器(DAC),将数字波形转换为模拟波形。

4. 频率分辨率和采样率:DDS正弦信号发生器的性能在很大程度上取决于频率分辨率和采样率。设计者需要在可实现的范围内尽量提高这两项指标,以满足高速度和高精度的需求。

5. FPGA平台选择:基于FPGA的DDS正弦信号发生器设计需要选择合适的FPGA平台。这包括考虑FPGA的逻辑单元数量、存储资源、时钟频率、I/O引脚数量和速率等。

6. 相位噪声优化:相位噪声是影响正弦信号质量的重要因素。设计时要考虑到如何通过优化算法和硬件设计来降低相位噪声。

7. 软件和硬件协同设计:在基于FPGA的设计中,软件和硬件是紧密结合的。开发人员需要利用硬件描述语言(如VHDL或Verilog)编写FPGA配置代码,并通过专业的开发工具进行编译和综合。同时,软件设计人员需要编写上层的控制软件以实现对信号发生器的控制和管理。

8. 系统集成与测试:设计完成后,需要对FPGA上的DDS正弦信号发生器进行系统集成与测试,验证信号质量、频率范围、幅度控制等各项指标是否符合设计要求。

由于提供的文档内容是通过OCR技术扫描得到的文字,其中包含许多误识别和不完整的词汇,这可能反映了文档的质量不高或者是扫描过程中的问题。然而,根据提供的文件标题和描述,我们可以确定这是一个关于“基于FPGA的DDS正弦信号发生器”的技术文档,即使具体内容不够清晰,但我们依然可以提炼出上述的关键知识点。