本文介绍了一个基于CameraLink标准的数字图像处理系统的设计,涉及到的关键词包括DSP(数字信号处理器)、FPGA(现场可编程门阵列)以及CameraLink接口技术。在这篇论文中,作者详细阐述了如何利用FPGA和DSP的结合,设计出一个能够处理CameraLink协议输出信号的高速图像处理系统。下面将详细展开这些技术点和设计要素。

DSP+FPGA结合的数字图像处理系统因其编程灵活、算法简单、嵌入系统方便等特点,已经被广泛应用于电子领域。这些系统利用DSP的强大运算能力以及FPGA的高速逻辑控制能力,实现了图像处理过程中的复杂计算和快速数据处理。在实时图像处理的背景下,系统需要处理大量数据,且要求高相关性和严格的帧、场时间限制,因此对运算能力的要求非常高。

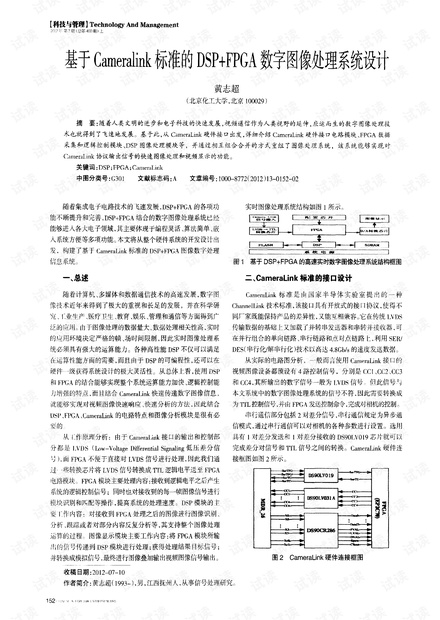

在CameraLink标准的接口设计方面,CameraLink是一种基于ChannelLink技术的标准,拥有开放的接口协议,使得不同厂家的产品能够保持各自的差异性的同时实现互相兼容。CameraLink通过使用SER/DES技术,在并行组合的单向链路、串行链路和点对点链路中,可以达到高达4.8Gb/s的数据传输速度。CameraLink的硬件接口输出通常是低压差分信号(LVDS),而FPGA模块处理的是TTL(晶体管-晶体管逻辑)信号,因此需要使用转换芯片将LVDS信号转换成TTL信号,以方便FPGA进行后续处理。

FPGA模块在这个系统中扮演着重要的角色,主要包括接收逻辑电平后产生系统逻辑控制信号,以及对接收到的图像信号进行模块识别和匹配操作,从而提高系统处理速度。FPGA的灵活性允许设计者根据需求定制硬件功能,实现复杂的信号处理算法。

DSP模块则负责对经过FPGA处理后的图像数据进行深入的图像识别、分析、跟踪等操作,支持整个图像处理运算过程。DSP的可编程性和强大的计算能力使得它能够快速响应并分析视频图像数据。

图像显示模块则将FPGA处理后的信号传递到DSP模块进行更深入的处理,然后将处理结果转换成模拟信号,通过视频叠加输出视频图像信号。这一部分涉及到视频信号的数字到模拟的转换过程,保证了处理后的图像能够被常规的显示设备所接收和展示。

文章中还提供了系统结构图,描述了基于CameraLink标准的DSP+FPGA数字图像处理系统的架构。系统主要由FPGA数据采集和逻辑控制模块、DSP图像处理模块以及图像显示模块组成,这些模块共同协作,实现对CameraLink协议输出信号的快速图像处理和视频显示功能。

该论文详细介绍了基于CameraLink标准的DSP+FPGA数字图像处理系统的硬件设计和接口设计方法,强调了系统在实时图像处理中的应用价值以及高速数据传输能力。通过利用DSP和FPGA的优点,系统能够实现复杂图像处理算法的快速执行和视频图像的实时显示。